This is the post-print version of the original article published in the proceedings of the 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 77-80 (2017) (http://dx.doi.org/10.23919/SISPAD.2017.8085268)

# 3D Simulation of Silicon-Based Single-Electron Transistors

F. J. Klüpfel, P. Pichler Fraunhofer Institute for Integrated Systems and Device Technology IISB Erlangen, Germany fabian.kluepfel@iisb.fraunhofer.de

*Abstract*—Single electron transistors based on silicon nanopillars were investigated with regard to their current voltage characteristics. The simulations make use of the commercial quantum simulator nextnano++, but extend its functionality for the calculation of tunneling currents. A comparison with results obtained by the Monte-Carlo based tunneling simulator SIMON is presented. Investigations include the variation of geometrical quantities and quantum dot doping.

Keywords—quantum dot; single electron transistor; numerical simulation

#### I. INTRODUCTION

A silicon quantum dot in an insulating matrix can trap electrons or holes. Charge carriers enter or leave the dot via tunneling from nearby conductive electrodes. The tunneling rates, strongly influenced by the insulator thickness between dot and electrode, determine the time constants of the trapping process. A notable effect is the Coulomb blockade, which prevents subsequent carriers from entering an already occupied quantum dot. The blockade is caused mainly by electrostatic repulsion and enforces sequential tunneling of carriers when two tunneling junctions with different electrostatic potential are close to the dot.

Single electron transistors (SETs) make use of the Coulomb blockade and have been proposed for low power electronics and improved integration density of beyond-CMOS electronics [1]. Usually, two electrodes (source and drain) are close enough to the dot in order to enable tunneling, while the third electrode (gate), distant enough to prevent tunneling, shifts the electrostatic potential of the dot. A characteristic feature of SETs compared to usual field-effect transistors (FETs) is an oscillation of the source-drain current when the gate voltage is varied. Because of this, electrical characteristics SETs should not be considered as a direct replacement for FETs. Instead, proposed applications make use of the special features of SETs to realize very low voltage inverters [2] or multi-value storage cells [3]. Due to the very low tunneling currents necessary for low-power operation of SETs, hybrid circuits with SETs for logic or storage operation and with FETs for providing driving currents are envisioned [4].

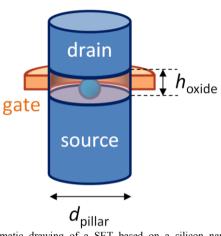

Fig. 1: Schematic drawing of a SET based on a silicon nanopillar with embedded oxide layer. The front of the all-around gate has been removed in order to open the view on the quantum dot centered in the oxide layer of the nanopillar.

For the integration of SET electronics with classical CMOS, SET fabrication should use processing steps compatible with CMOS. Additionally, using established technologies should give better control of the critical nanostructuring steps during SET fabrication. Very important is the accurate positioning of the quantum dot with respect to the electrodes, in order to obtain reproducible device characteristics. The EU project IONS4SET [5] proposes a design based on quantum dot self-assembly in a silicon nanopillar. The structure is shown schematically in Fig. 1. It employs a vertical silicon nanopillar with an embedded oxide layer of thickness  $h_{\text{oxide}}$ , in which a silicon nanodot with diameter  $d_{dot}$  is formed by ion irradiation and subsequent phase separation by thermal treatment [6]. A ring-like allaround gate controls current flow through the pillar. The structure consists solely of silicon and silicon oxide materials. The electrodes source, drain, and gate should be highly doped in order to avoid parasitic resistances. Except for the embedded oxide layer with the nanodot, the device structure is similar to vertical silicon nanowire FETs, which have been demonstrated experimentally and are expected to enter commercial products within few years [7]. This makes the fabrication of the proposed SET structures feasible and most suitable for the integration with future CMOS technology.

The research leading to these results has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 688072 IONS4SET.

### II. SIMULATION APPROACH

For the theoretical description, the commercial circuit simulator SIMON [8] based on the so-called orthodox theory is frequently employed. SIMON employs the Monte-Carlo method to simulate circuits consisting of tunnel junctions combined with classical circuit elements. This method as well as compact models developed for SETs (e.g. [9]-[11]) are dependent on input from experiment or other simulation methods in order to obtain model parameters like capacitances and tunnel resistances. Geometrical variations and material properties cannot be taken into account directly. Thus, for evaluation and optimization of SETs with advanced 3D structures and non-metallic materials, a 3D simulator analog to commercial general-purpose device simulators would be desirable. However, such an out-of-the-box solution is not available to the best of our knowledge.

We have developed a SET simulator based on the commercial simulator nextnano++ [12], which solves the coupled 3D Schrödinger and Poisson equations. It provides a reliable way to obtain electrostatics, wave functions and energy levels for arbitrary geometries and different material combinations. Compared to previously reported 3D approaches for the calculation of SET characteristics (e.g. [13], [14]) we can make use of the extensive functionality of nextnano++, including predefined shapes for structure generation, a material database, use of dopants, and positioning of fixed charges. nextnano++ does not provide the possibility to place a specific number of charge carriers on the quantum dot. However, this requirement can be fulfilled by adjusting the dot Fermi level until the desired charge state is reached. Our simulator uses batch execution of nextnano++ in order to obtain wave functions, energy levels and electrostatic potential for all required bias and charge states. Subsequently, tunneling rates are calculated via the approach described by See et al. [13], who provide an analytical description of the electrode wave function and calculate matrix elements according to Bardeen's equation. For the formulation of the

electrode wave functions, source and drain are approximated as infinite planar surfaces. For very low pillar diameters the radial confinement leads to a concentration of carriers in the middle of the pillar and shifts the conduction band minimum to higher energies. 2D simulation of a circular quantum well with nextnano++ shows that this energy shift is around 30 mV for a pillar diameter of 10 nm. An additional broadening of the current peaks must be expected due to the formation of subbands within the electrodes, which leads to a wider energy distribution of occupied states in the source electrode. These electrode confinement effects are not included in the presented calculations and could be implemented in future versions of our software. The tunneling current between source and drain is determined via the master equation formalism. Leakage currents between the electrodes due to tunneling without assistance of the quantum dot states have not been included in the model so far.

#### **III. SIMULATION RESULTS**

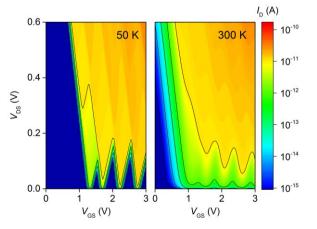

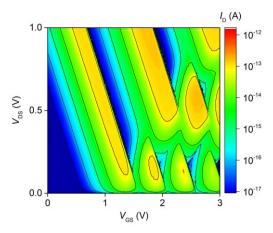

To get a base line for the performance of our SET structure, we start with assuming metal source and drain contacts. In the limit of 0 K all quantum dot energy levels between the source and drain Fermi levels can contribute to the tunneling current. This leads to the terrace-like current voltage characteristics shown in Fig. 2 for 50 K. The current increases stepwise for increasing drain voltage, as more and more energy levels contribute to the current. Similar to FETs, there is an off-regime for low gate voltages, where no current is flowing between source and drain. The threshold voltage is determined by the gate capacitance in relation to the total capacitance of the quantum dot as well as the confinement energy of electrons within the dot. The current-voltage diagram for 50 K in Fig. 2 exhibits triangular regions without current flow at low drain voltages and low temperature. These lead to the characteristic current oscillations of a SET for increasing gate voltage. At room temperature these features are smoothed out, but are still observable. The simulation at 50 K shows that the first oscillation period is narrower than

Fig. 2: IV characteristics of a SET with metal electrodes and a silicon quantum dot, simulated for a dot diameter of  $d_{dot}=3$  nm,  $h_{oxide}=6$  nm,  $d_{pillar}=10$  nm. Temperature is 50 K (left) and 300 K (right).

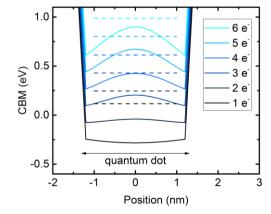

Fig. 3: Conduction band minimum (CBM, solid) and ground state energy (dashed) along the SET symmetry axis for different electron numbers on the quantum dot as calculated with nextnano+++ for T = 50 K,  $V_{DS} = 0$  V,  $V_{GS} = 1$  V.

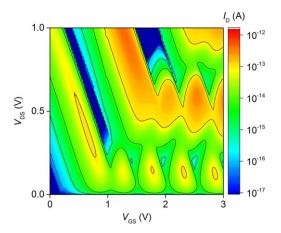

Fig. 4: IV characteristics of a SET with highly doped silicon electrodes and a silicon quantum dot, simulated for  $d_{dot}=3$  nm,  $h_{oxide}=6$  nm,  $d_{pillar}=10$  nm, and T=300 K.

the subsequent periods. The explanation is given by Fig. 3, which shows the energy landscape depending on the number of electrons on the quantum dot. The ground state for the first electron has a lower energetic distance to the ground state of the second electron compared to higher electron numbers. This is due to the shape of the conduction band minimum, which is convex for the first electron but concave for higher electron numbers.

A silicon source electrode provides only a narrow energy range of filled conduction band states, from which electrons can tunnel to the quantum dot. Thus, only dot energy levels well aligned with the source conduction band minimum contribute to the tunneling current. Fig. 4 demonstrates that this leads to more pronounced oscillations even at room temperature. However, current levels are lower compared to a SET with similar geometry and metal electrodes, as shown before in Fig. 2. The fragmented appearance of the IV characteristics stems from the dot energy levels, which shift continuously with the applied voltages, but change their energetic position abruptly when the number of charge carriers on the dot varies.

We compared the results from 3D SET simulations with simulations conducted with SIMON. The most important model parameters are the total capacitance of the quantum dot, the gate-to-dot capacitance, the dot energy levels, and the tunneling resistance of the junctions. The energy levels are a direct output of nextnano++, while capacitances can be extracted from nextnano++ simulations via the change of the ground state energy with respect to variations of external voltages and the dot charge state. The tunneling resistance was used as free parameter to adjust the absolute current level. It should be noted, that SIMON's graphical user interface does not allow entering a sufficient number of energy levels in order to account for the correct degeneracy of the levels. However, it is possible to enter a larger number of energy levels directly into the command file generated by the user

Fig. 5: SET simulation with SIMON 2.0, model parameters extracted from Fig. 4.

interface and to run the simulation from the command line. Comparison of Fig. 4 and Fig 5 demonstrates qualitative agreement of the nextnano++ based simulations with SIMON calculations. However, the results from SIMON are more regular due to a simpler model which does not account for bias-dependent changes in potential shape and dot energy levels. Especially the assumption of a constant total capacitance of the quantum dot makes it impossible to account for the unequal spacing of ground states for different dot charge states as shown in Fig. 3.

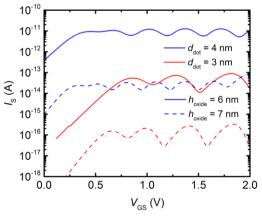

A strength of our method is the ability to vary the geometry of the SETs directly, which provides the possibility to optimize the device properties with respect to target specifications. In Fig. 6 different options for dot diameter and oxide thickness are compared. It can be seen that the dot diameter determines the oscillation period of the current. However, the absolute current level is not determined by  $d_{dot}$  alone, but by the distance between dot and electrodes. This corresponds to the thickness of the tunneling barrier and is

Fig. 6: Transfer characteristics for variations of quantum dot diameter and oxide thickness. The electrodes consist of highly doped silicon, the temperature is 300 K and the pillar diameter equals 10 nm.

given by  $(h_{\text{oxide}}-d_{\text{dot}})/2$ . In order to obtain strong oscillations at room temperature with measureable current levels, both dot diameter and oxide thickness should be reduced as much as technologically feasible.

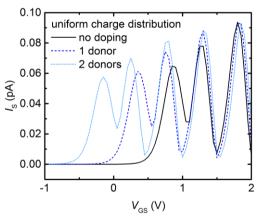

A question not explored experimentally so far is the influence of dopants within the quantum dot on SET characteristics. If the SET electrodes consist of doped silicon, it is difficult to avoid the contamination of the dot with dopant atoms. It was reported that phosphorous tends to accumulate in or at Si nanocrystals embedded in SiO<sub>2</sub>, reaching P concentrations far above the bulk solubility level [15]. On the other hand, recent results indicate that activation of P in Si nanocrystals is far below 1% [16]. A clear indication of active dopants on the SET quantum dot would be desirable for improving the basic understanding of the doping of nanostructures. When dot doping cannot be avoided completely, future SET circuits must be designed tolerant to fluctuations of the number of active dopants.

The effect of active dopants on the quantum dot can be simulated by assuming fixed charges on the dot. We compared simulations with point-like charges at the dot surface with simulations employing a uniform charge distribution of the same integrated charge within the dot (not shown here). For a dot diameter of 3 nm, the only difference was in the absolute current levels, while threshold voltage and current oscillations were not affected by the placement of the charges. Fig. 7 demonstrates the influence of active donors on the SET transfer characteristics by using uniform distributions of positive charge on the dot. The threshold voltage is shifted by about 0.5 V per dopant atom, while the oscillation period remains unchanged. The current peaks at high gate voltages overlap, which would make operation in this regime relatively tolerant to dopant fluctuations between different devices.

Fig. 7: Influence of dot doping on the SET transfer characteristic. Electrically active donors are simulated as positive charges uniformly distributed over the dot.

## IV. SUMMARY

SETs fabricated from silicon nanopillars with embedded silicon oxide tunneling barriers and spherical silicon quantum dots were investigated by numerical simulation. For the accurate description of electrostatics, quantized energy levels, and the corresponding wave functions the simulator nextnano++ was employed. Current voltage characteristics were calculated from the nextnano++ results and are used for optimization of the SET geometry. Model parameters for the Monte-Carlo based simulator SIMON can be extracted from our simulations and lead to qualitatively similar results. We demonstrated that active dopants on the quantum dot may have a strong effect on the device characteristics and should be avoided whenever possible. Otherwise, circuits tolerant to dopant variations between the constituent SETs need to be developed.

- Y. Takahashi, Y. Ono, A. Fujiwara and H. Inokawa, "Silicon singleelectron devices", J. Phys.: Cond. Matter, vol. 14, pp. R995, 2002.

- [2] A. M. Ionescu, M. J. Declercq, S. Mahapatra, K. Banerjee, and J. Gautier, "Few electron devices: towards hybrid CMOS-SET integrated circuits," in *Proceedings of 39th Design Automation Conference*, 2002, pp. 88–93.

- [3] H. Inokawa, A. Fujiwara, and Y. Takahashi, "A multiple-valued singleelectron SRAM by the PADOX process," in 6th International Conference on Solid-State and IC Technology, pp. 205–208.

- [4] R. Parekh, A. Beaumont, J. Beauvais, and D. Drouin, "Simulation and Design Methodology for Hybrid SET-CMOS Integrated Logic at 22-nm Room-Temperature Operation," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 918–923, 2012.

- [5] www.ions4set.eu

- [6] B. Liedke, K.-H. Heinig, A. Mücklich, and B. Schmidt, "Formation and coarsening of sponge-like Si-SiO<sub>2</sub> nanocomposites", Appl. Phys. Lett., vol. 103, p. 133106, 2013.

- [7] International Roadmap for Devices and Systems, 2016 Edition, More Moore White Paper, irds.ieee.org

- [8] C. Wasshuber, H. Kosina, and S. Selberherr, "SIMON A Simulator for Single-Electron Tunnel Devices and Circuits", *IEEE Trans. on CAD of IC and Syst.*, vol. 16, pp. 937-944, 1997.

- [9] K. Uchida et al., "Analytical Single-Electron Transistor (SET) Model for Design and Analysis of Realistic SET Circuits," Jpn. J. Appl. Phys., vol. 39, no. Part 1, No. 4B, pp. 2321–2324, 2000.

- [10] Sang-Hoon Lee et al., "A practical SPICE model based on the physics and characteristics of realistic single-electron transistors," IEEE Trans. Nanotechnology, vol. 1, no. 4, pp. 226–232, 2002.

- [11] H. Inokawa and Y. Takahashi, "A compact analytical model for asymmetric single-electron tunneling transistors", *IEEE Trans. Electron Devices*, vol. 50, no. 2, pp. 455–461, 2003.

- [12] nextnano++: Version 2016\_04\_29\_RedHat\_67, nextnano GmbH, 2016.

- [13] J. Sée, P. Dollfus, S. Galdin, and P. Hesto, "From wave-functions to current-voltage characteristics: Overview of a Coulomb blockade device simulator using fundamental physical parameters", *J. Comput. Electron.*, vol. 5, no. 1, pp. 35–48, 2006.

- [14] F. O. Heinz, A. Schenk, A. Scholze, and W. Fichtner, "Full Quantum Simulation of Silicon-on-Insulator Single-Electron Devices", J. Comput. Electron., vol. 1, no. 1/2, pp. 161–164, 2002.

- [15] M. Perego et al., "Thermodynamic stability of high phosphorus concentration in silicon nanostructures," (eng), Nanoscale, vol. 7, no. 34, pp. 14469–14475, 2015.

- [16] S. Gutsch et al., "Electronic properties of phosphorus doped silicon nanocrystals embedded in SiO 2," Appl. Phys. Lett., vol. 106, no. 11, p. 113103, 2015.